# Optimizing Recovery Logic in Speculative High-Level Synthesis

Dylan Leothaud<sup>\*</sup>, Jean-Michel Gorius<sup>\*</sup>, Simon Rokicki<sup>\*</sup>, Steven Derrien<sup>†</sup>

\*Univ Rennes, Inria, CNRS, IRISA

†UBO, Lab-STICC

This work is partially funded by the French National Research Agency (ANR) as part of the LOTR project

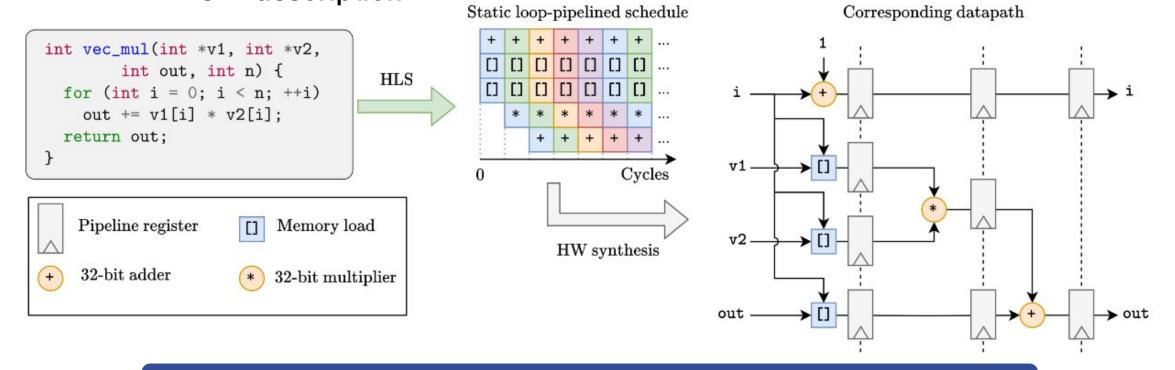

## **High-Level Synthesis**

High-Level Synthesis (HLS) tools generate HDL from C++ description

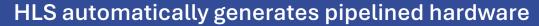

#### What can I use HLS for in 2025

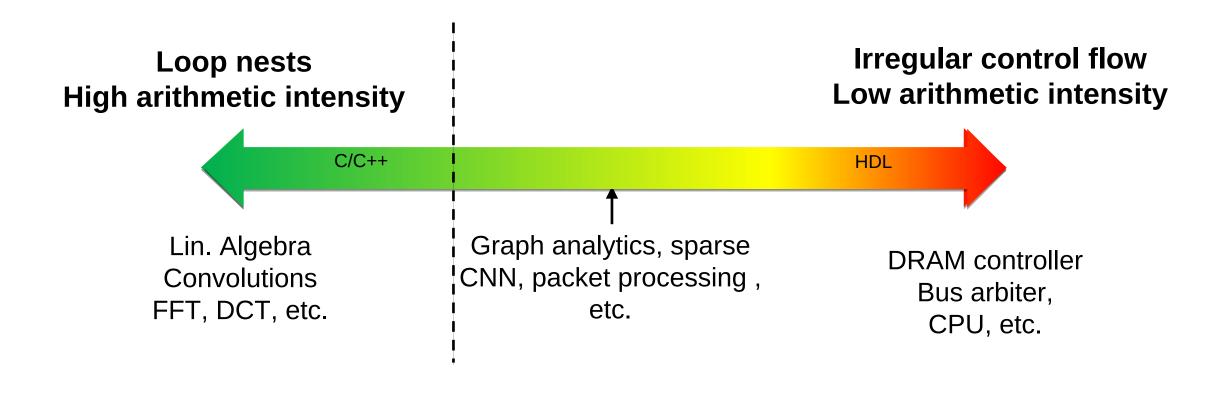

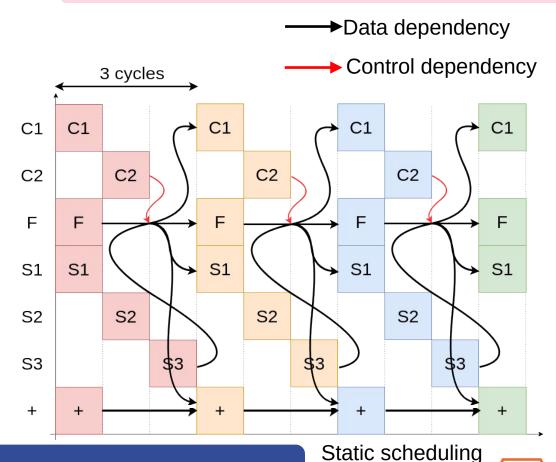

# Static scheduling

# SOTA commercial HLS tools all rely on static scheduling

while (1) {

y = y + x;

// 2 cycles

if (C(x)) {

// 1 cycle

x = F(x);

} else {

// 3 cycles

x = S(x);

}

}

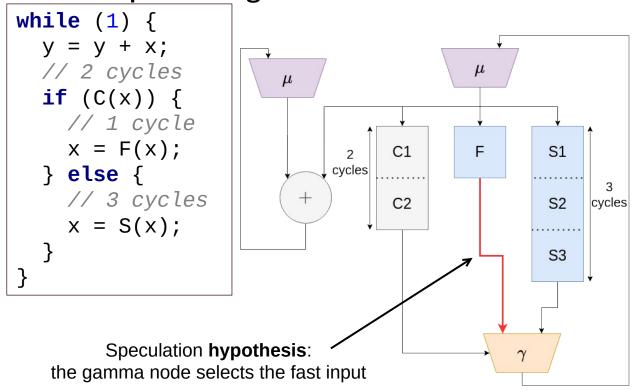

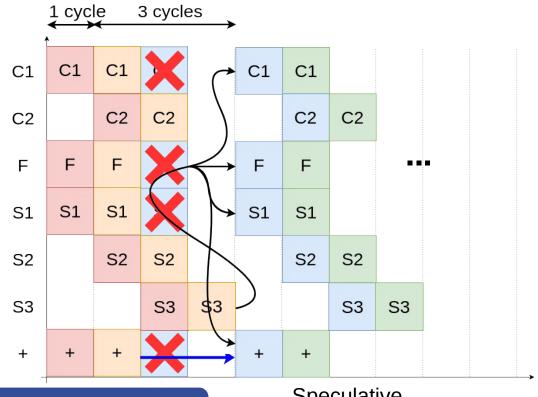

# Speculative scheduling

Speculative scheduling starts future iterations by predicting control-flow decisions

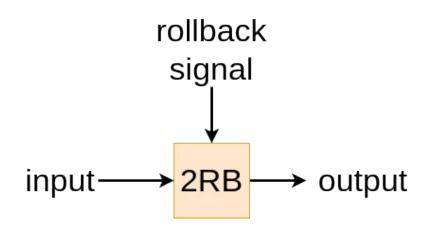

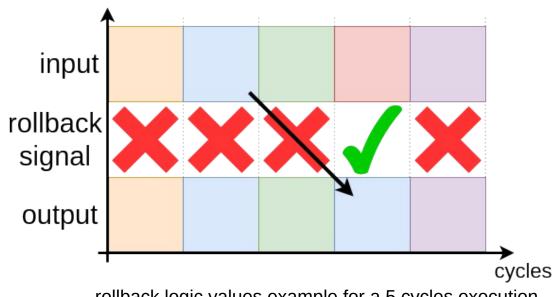

## Rollback logic behavior

rollback logic values example for a 5 cycles execution

## How to optimize rollback logic cost?

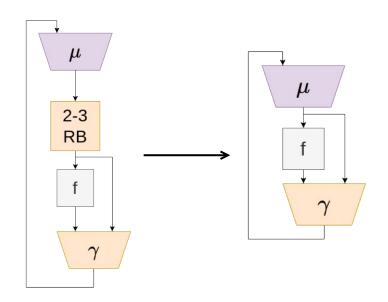

Remove rollback logic that can be proven unused

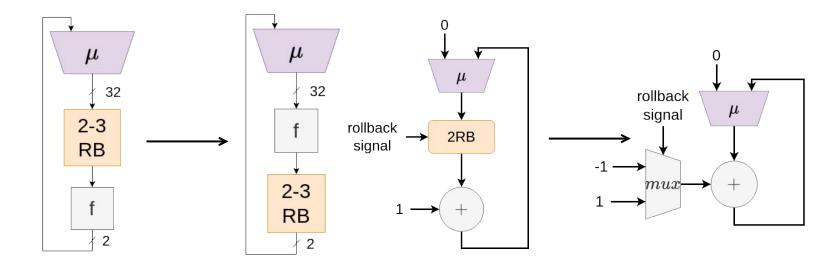

Retime rollback logics to minimal bitwidth values

Reuse reversible operations' operators

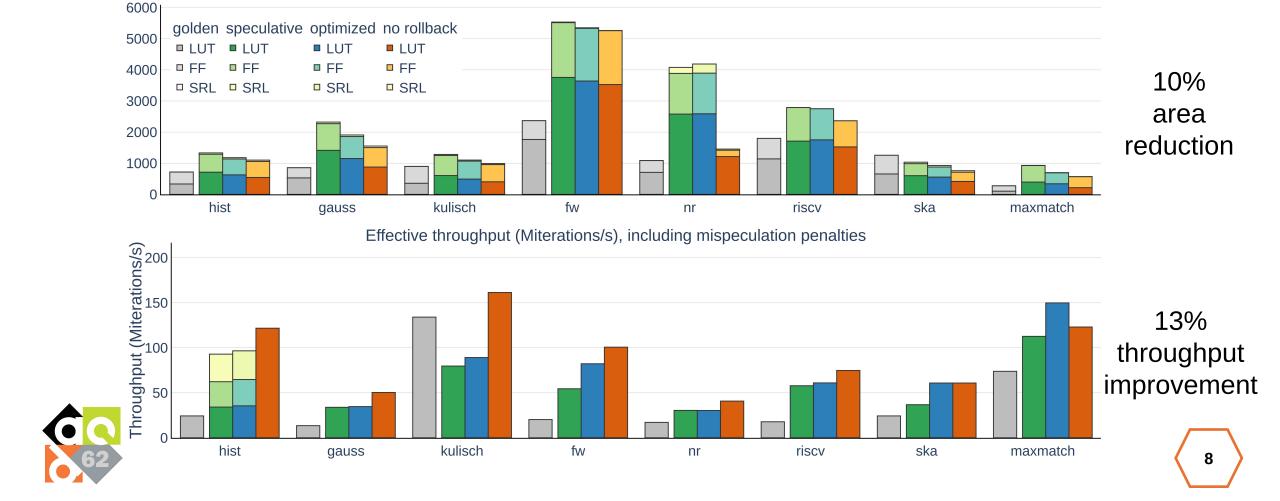

## **Experimental results**

Resource utilization for each benchmark

#### Conclusion

Speculation opens up new opportunities for High-Level Synthesis

One challenge is to minimize rollback logic overhead

With our approach, it is possible to decrease the speculative circuit area and increase the clock frequency